## **MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY**

Autonomous Institution – UGC, Govt. of India

# Department of CSE (Artificial Intelligence and Machine Learning)

B. TECH (R-24 Regulation) (II YEAR – I SEM)

# 2025-26

COMPUTER ORGANIZATION AND ARCHITECTURE (R24A0561)

# **LECTURE NOTES**

### MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY

(Autonomous Institution – UGC, Govt. of India)

Recognized under 2(f) and 12(B) of UGC ACT 1956

(Affiliated to JNTUH, Hyderabad, Approved by AICTE-Accredited by NBA & NAAC – 'A' Grade - ISO 9001:2015 Certified) Maisammaguda, Dhulapally (Post Via. Hakimpet), Secunderabad–500100, Telangana State, India

## Department of Computer Science and Engineering (Artificial Intelligence and Machine Learning)

#### Vision

To be a premier center for academic excellence and research through innovative interdisciplinary collaborations and making significant contributions to the community, organizations, and society as a whole.

#### Mission

- To impart cutting-edge Artificial Intelligence technology in accordance with industry norms.

- To instil in students a desire to conduct research in order to tackle challenging technical problems for industry by sustaining the ethical values.

- To develop effective graduates who are responsible for their professional growth, leadership qualities and are committed to lifelong learning.

#### **QUALITY POLICY**

- To provide sophisticated technical infrastructure and to inspire students to reach their full potential.

- To provide students with a solid academic and research environment for a comprehensive learning experience.

- To provide research development, consulting, testing, and customized training to satisfy specific industrial demands, thereby encouraging self-employment and entrepreneurship among students.

For more information: www.mrcet.ac.in

#### MALLA REDDY COLLEGE OF ENGINEERING AND TECHNOLOGY

#### II year B.Tech. CSE-I Sem

L/T/P/C 3/1/0/4

#### (R24A0561) COMPUTER ORGANIZATION AND ARCHITECTURE

#### **COURSE OBJECTIVES:**

#### **Course Objectives**

• The purpose of the course is to introduce principles of computer organization and the basic architectural concepts.

• It begins with basic organization, design, and programming of a simple digital computer and introduces simple register transfer language to specify various computer operations.

• Topics include computer arithmetic, instruction set design, microprogrammed control unit, pipelining and vector processing, memory organization and I/O systems, and multiprocessors

#### UNIT - I

Digital Computers: Introduction, Block diagram of Digital Computer, Definition of Computer Organization, Computer Design and Computer Architecture.

Register Transfer Language and Micro operations: Register Transfer language, Register Transfer, Bus and memory transfers, Arithmetic Micro operations, logic micro operations, shift micro operations, Arithmetic logic shift unit.

Basic Computer Organization and Design: Instruction codes, Computer Registers Computer instructions, Timing and Control, Instruction cycle, Memory Reference Instructions, Input – Output and Interrupt.

#### UNIT - II

Microprogrammed Control: Control memory, Address sequencing, micro program example, design of control unit.

Central Processing Unit: General Register Organization, Instruction Formats, Addressing modes, Data Transfer and Manipulation, Program Control.

#### UNIT - III

Data Representation: Data types, Complements, Fixed Point Representation, Floating Point Representation.

Computer Arithmetic: Addition and subtraction, multiplication Algorithms, Division Algorithms, Floating – point Arithmetic operations. Decimal Arithmetic unit, Decimal Arithmetic operations.

#### $\mathbf{UNIT} - \mathbf{IV}$

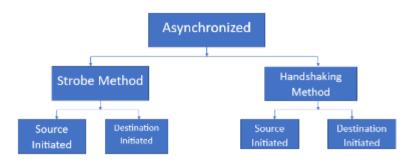

Input-Output Organization: Input-Output Interface, Asynchronous data transfer, Modes of Transfer, Priority Interrupt Direct memory Access.

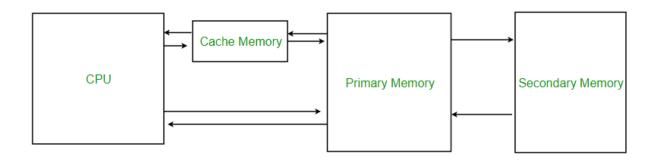

Memory Organization: Memory Hierarchy, Main Memory, Auxiliary memory, Associate Memory, Cache Memory.

#### UNIT - V

Reduced Instruction Set Computer: CISC Characteristics, RISC Characteristics.

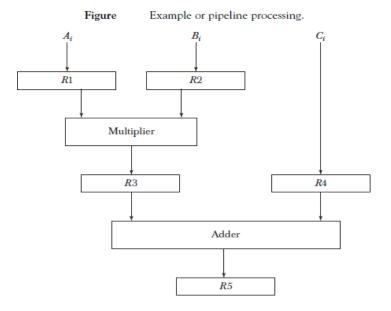

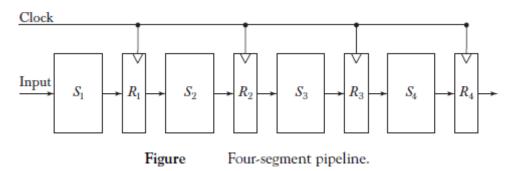

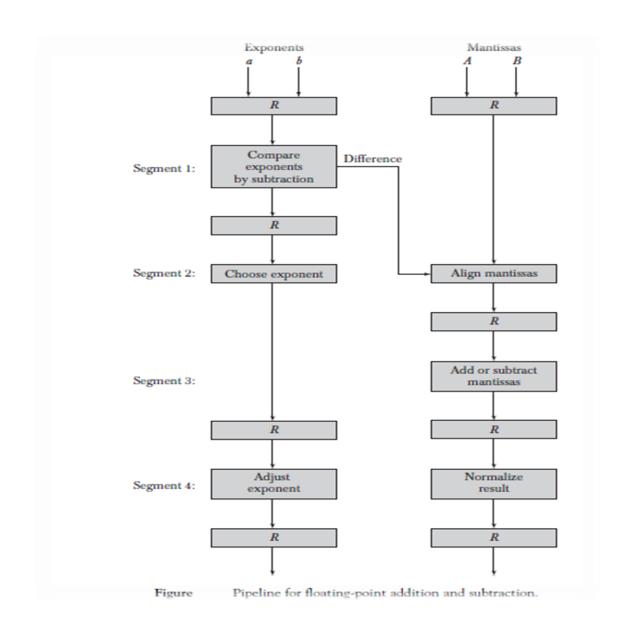

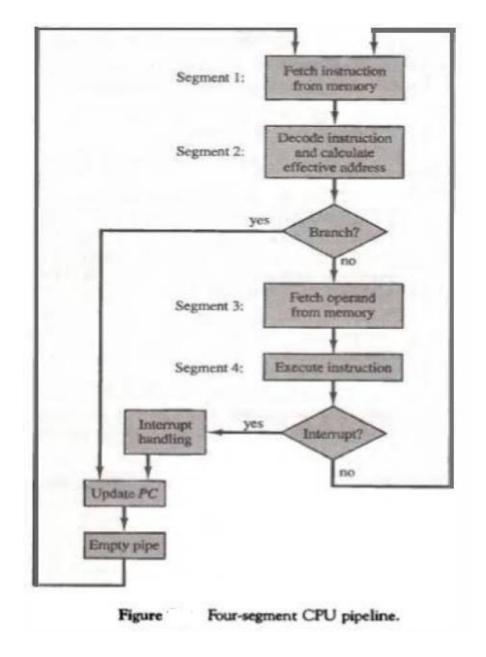

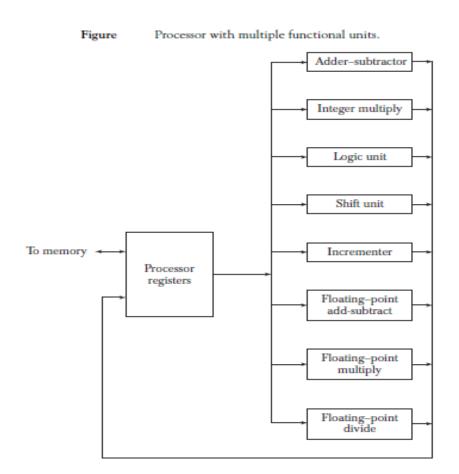

Pipeline and Vector Processing: Parallel Processing, Pipelining, Arithmetic Pipeline, Instruction Pipeline, RISC Pipeline, Vector Processing, Array Processor.

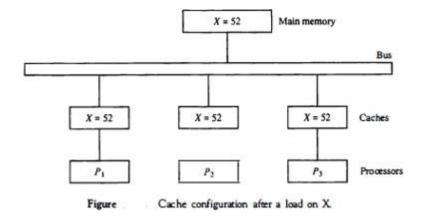

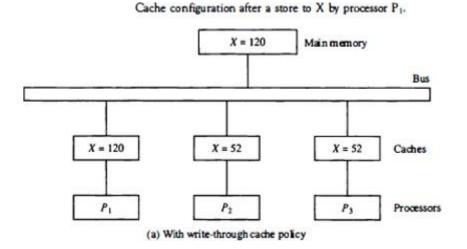

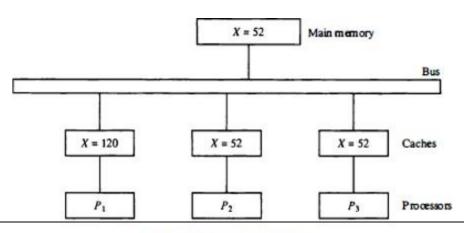

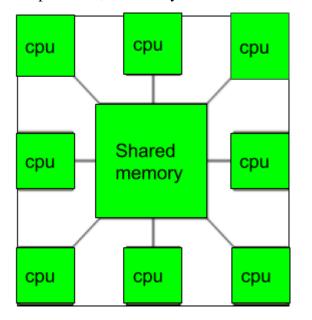

Multi Processors: Characteristics of Multiprocessors, Interconnection Structures, Inter processor arbitration, Inter processor communication and synchronization, Cache Coherence.

#### **TEXT BOOK:**

1. Computer System Architecture - M. Morris Mano, Third Edition, Pearson/PHI.

#### **REFERENCE BOOKS:**

1. Computer Organization – Carl Hamacher, Zvonks Vranesic, SafeaZaky, V th Edition, McGraw Hill.

2. Computer Organization and Architecture – William Stallings Sixth Edition, Pearson/PHI.

3. Structured Computer Organization – Andrew S. Tanenbaum, 4 th Edition, PHI/Pearson.

#### **COURSE OUTCOMES:**

• Understand the basics of instruction sets and their impact on processor design.

• Demonstrate an understanding of the design of the functional units of a digital computer system.

• Evaluate cost performance and design trade-offs in designing and constructing a computer processor including memory.

• Design a pipeline for consistent execution of instructions with minimum hazards. Recognize and manipulate representations of numbers stored in digital computers

## MALLA REDDY COLLEGE OF ENGINEERING AND TECHNOLOGY CSE (Artificial Intelligence and Machine Learning)

#### INDEX

| S.No | Unit | Торіс                                                                                                                                                                                                                                        | P. No |  |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|

| 1    | Ι    | Introduction to big data: Data, Characteristics of data                                                                                                                                                                                      |       |  |

| 2    | Ι    | Digital Computers: Introduction, Block diagram of Digital Computer,<br>Definition of Computer Organization, Computer Design and Computer<br>Architecture.                                                                                    |       |  |

| 3    | Ι    | Register Transfer Language and Micro operations: Register Transfer<br>language, Register Transfer, Bus and memory transfers, Arithmetic Micro<br>operations, logic micro operations, shift micro operations, Arithmetic logic<br>shift unit. |       |  |

| 4    | Ι    | Basic Computer Organization and Design: Instruction codes, Computer<br>Registers Computer instructions, Timing and Control, Instruction cycle,<br>Memory Reference Instructions, Input – Output and Interrupt                                | 5     |  |

| 5    | Π    | Microprogrammed Control: Control memory, Address sequencing, micro program example, design of control unit                                                                                                                                   | 9     |  |

| 6    | Π    | Central Processing Unit: General Register Organization, Instruction<br>Formats, Addressing modes, DataTransfer and Manipulation, Program<br>Control                                                                                          | 15    |  |

| 7    | III  | Data Representation: Data types, Complements, Fixed Point<br>Representation, Floating Point Representation.                                                                                                                                  | 33    |  |

| 8    | III  | Computer Arithmetic: Addition and subtraction, multiplication<br>Algorithms, Division Algorithms                                                                                                                                             |       |  |

| 9    | III  | Floating – point Arithmetic operations. Decimal Arithmetic unit, Decimal Arithmetic operations.                                                                                                                                              | 52    |  |

| 10   | IV   | Input-Output Organization: Input-Output Interface, Asynchronous data transfer, Modes of Transfer, Priority Interrupt Direct memory Access.                                                                                                   | 55    |  |

| 11   | IV   | Memory Organization: Memory Hierarchy, Main Memory, Auxiliary<br>memory, Associate Memory, CacheMemory                                                                                                                                       | 61    |  |

| 12   | v    | Reduced Instruction Set Computer: CISC Characteristics, RISC Characteristics.                                                                                                                                                                | 63    |  |

| 13   | V    | Pipeline and Vector Processing: Parallel Processing, Pipelining, Arithmetic<br>Pipeline, Instruction Pipeline, RISC Pipeline, Vector Processing, Array<br>Processor.                                                                         | 64    |  |

| 14   | V    | Multi Processors: Characteristics of Multiprocessors, Interconnection<br>Structures, Inter processor arbitration, Inter processor communication and<br>synchronization, Cache Coherence.                                                     | 77    |  |

#### UNIT - I

**Digital Computers:** Introduction, Block diagram of Digital Computer, Definition of Computer Organization, Computer Design and Computer Architecture.

**Register Transfer Language and Micro operations:** Register Transfer language, Register Transfer, Bus and memory transfers, Arithmetic Micro operations, logic micro operations, shift micro operations, Arithmetic logic shift unit.

**Basic Computer Organization and Design**: Instruction codes, Computer Registers Computer instructions, Timing and Control, Instruction cycle, Memory Reference Instructions, Input – Output and Interrupt.

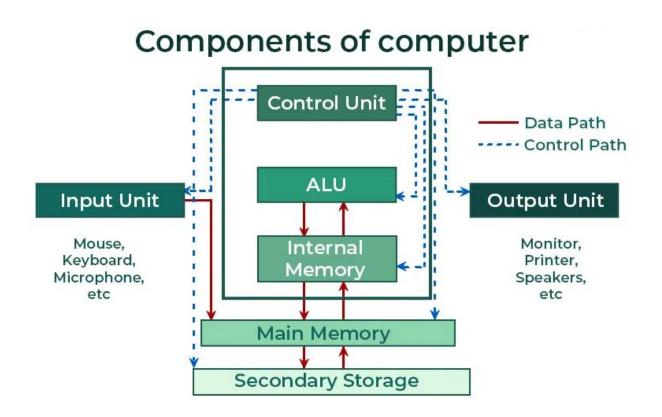

The functional components of a digital computer include the Input Unit, which takes in data; the CPU, which processes data with its Control Unit (CU), Arithmetic Logic Unit (ALU), and Registers; the Memory Unit, which stores data temporarily (RAM) or permanently (HDD/SSD); the Output Unit, which displays results; and the Bus System, which connects and transfers data between components. These parts work together to execute tasks and provide results.

The **functional components of a computer** are the key parts that work together to process and manage data. These include the **Input Unit** for receiving data, the **CPU** for processing it, the **Memory Unit** for storing information, the **Output Unit** for displaying results, and the **Bus System** that connects all parts. These components help the computer perform tasks efficiently.

#### 1. Input Unit

- **Purpose:** Captures data and instructions from users or external sources.

- Function: Converts user input into binary signals that the computer can process.

- Common Devices (2025):

- Keyboard, Mouse, Touchscreens

- Scanners, Sensors, Stylus pens

- Voice Assistants (e.g., Siri, Alexa)

- Biometric devices (face/fingerprint recognition)

- Iot-based inputs from smart devices

#### 2. Central Processing Unit (CPU) – The Brain of the Computer

The **CPU** executes instructions and controls all internal operations. In 2025, CPUs will often have multiple **cores** and **threads** to handle parallel processing efficiently. **Components of CPU:**

#### a. Arithmetic Logic Unit (ALU)

- Performs arithmetic operations (add, subtract, multiply, divide).

- Handles logical operations (comparison, decision-making).

- Supports AI/ML tasks using built-in vector/matrix operations (in modern CPUs).

#### **b.** Control Unit (CU)

- Directs the operations of all computer parts.

- Decodes instructions and coordinates data flow.

- Sends control signals to memory and I/O devices.

#### c. Registers

- High-speed memory locations within the CPU.

- Temporarily store instructions, addresses, and intermediate data.

- Examples: Accumulator, Instruction Register, Program Counter, Address Register.

- Modern CPUs include 64-bit or even 128-bit registers for faster processing.

#### 3. Memory / Storage Unit

The **memory unit** holds data and instructions before, during, and after processing. **a. Primary Memory (Main Memory):**

- RAM (Random Access Memory): Temporarily stores data during execution.

- Types in 2025: DDR5, LPDDR5X, and emerging **MRAM**.

- ROM (Read-Only Memory): Stores boot-up instructions and firmware.

- Cache Memory: Ultra-fast memory between CPU and RAM (L1, L2, L3 levels).

#### **b. Secondary Storage:**

- Used for long-term data storage.

- Examples: SSDs (NVMe drives), HDDs, flash drives, and cloud storage.

- Modern Trend: Use of Cloud Integration and hybrid storage models.

#### 4. Output Unit

- **Purpose:** Converts processed data (binary) into a form users can understand.

- Examples:

- Visual: Monitors (LED, OLED, 4K/8K displays)

- Print: Printers (Inkjet, Laser, 3D Printers)

- Audio: Speakers, Headphones

- Haptic: Vibration feedback devices

Computer Organization and Architecture is used to design computer systems.

• **Computer architecture** is about designing a computer system to balance performance, efficiency, cost, and reliability. It describes how a system is built from its components. This can be a high-level overview or a detailed explanation, including the instruction set architecture, micro architecture, logic design, and implementation.

• **Computer Organization** is about how the components of a computer system, like the CPU, memory, and input/output devices, are connected and work together to execute programs. It focuses on the operational aspects and how hardware components are implemented to support the architecture.

#### **Register Transfer Language (RTL):**

Register Transfer Language (<u>RTL</u>) is a low-level language that is used to describe the functioning of a digital circuit and, more specifically, the transfer of information between registers. It provides how data moves from one register to the other and how data is processed within the digital system. Through RTL, there is a capability of creating abstraction levels where high-level design descriptions can be created and easily linked to low-level hardware implementation in designing, simulating, as well as synthesizing digital circuits.

#### **Register Transfer Operations**

The operation performed on the data stored in the registers are referred to as register transfer operations.

There are different types of register transfer operations:

#### 1. Simple Transfer - R2 <- R1

The content of R1 are copied into R2 without affecting the content of R1. It is an unconditional type of transfer operation.

#### 2. Conditional Transfer

It indicates that if P=1, then the content of R1 is transferred to R2. It is a unidirectional operation.

#### 3. Simultaneous Operations

If 2 or more operations are to occur simultaneously then they are separated with comma (,). If the control function P=1, then load the content of R1 into R2 and at the same clock load the content of R2 into R1.

#### Advantages of Register Transfer Language (RTL)

- Enables efficient hardware design.

- This makes it possible to simulate some activities and perhaps detect some errors at an early date.

- Implements conceptual description up to the gate-level hardware.

- It helps to reuse the design components.

- It gives a clear guide on how to do timing analysis on a given design.

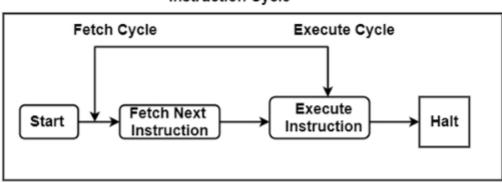

In basic computer organization, an instruction is a binary code that tells the computer what operation to perform and where to find the data. It's a fundamental unit of a program, specifying the actions the CPU must execute. The instruction cycle, also known as the fetch-decode-execute cycle, is the process by which the CPU handles each instruction.

Elaboration:

#### • Instruction Structure:

A basic instruction typically consists of an <u>opcode</u> (operation code) and an <u>address</u> <u>field</u>. The opcode specifies the operation to be performed (e.g., add, subtract, load, store). The address field indicates the location of the data or the next instruction.

#### • Instruction Cycle:

The instruction cycle involves several steps:

- 1. Fetch: The CPU retrieves the instruction from memory using the program counter.

- 2. **Decode:** The CPU interprets the opcode and determines the necessary actions.

- 3. **Execute:** The CPU performs the specified operation, which may involve reading or writing data from memory, using the <u>ALU</u>, and updating registers.

- <u>Instruction Types</u>:

- **Memory-reference instructions:** These instructions operate on data stored in memory, including addressing modes like direct and indirect addressing.

- **Register-reference instructions:** These instructions operate on data stored in processor registers, such as the accumulator.

- **Input/output instructions:** These instructions control the transfer of data between the computer and external devices.

#### Instruction Set Architecture (ISA):

The ISA defines the set of instructions that a CPU can execute. It essentially acts as an interface between the hardware and software, specifying what the processor can do and how it does it.

#### **Stored Program Concept:**

The computer stores both instructions and data in memory, allowing for flexible program execution and re-usability.

#### **Basics of Computer Organization and Design -**

In basic computer organization, an instruction is a binary code that tells the computer what operation to perform and where to find the data. It's a fundamental unit of a program, specifying the actions the CPU must execute. The instruction cycle, also known as the fetch-decode-execute cycle, is the process by which the CPU l

**Computer Organization** is about how the components of a computer system, like the CPU, memory, and input/output devices, are connected and work together to execute programs. It focuses on the operational aspects and how hardware components are implemented to support the architecture.

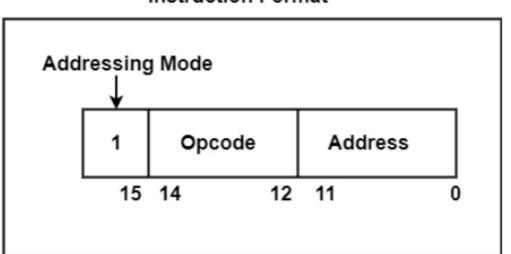

A <u>computer instruction</u> is a binary code that determines the micro-operations in a sequence for a computer. They are saved in the memory along with the information. Each computer has its specific group of instructions.

They can be categorized into two elements as Operation codes (Opcodes) and Address. Opcodes specify the operation for specific instructions. An address determines the registers or the areas that can be used for that operation. Operands are definite elements of computer instruction that show what information is to be operated on.

It consists of 12 bits of memory that are required to define the address as the memory includes 4096 words. The 15th bit of the instruction determines the addressing mode (where direct addressing corresponds to 0, indirect addressing corresponds to 1). Therefore, the instruction format includes 12 bits of address and 1 bit for the addressing mode, 3 bits are left for Opcodes.

The following block diagram shows the instruction format for a basic computer.

#### Instruction Format

# **Timing and Control**

- The timing for all registers in the basic computer is controlled by the master clock generator.

- The clock pulsed are applied to all the flip flops and registers in the system.

- The clock pulses do not change the state of register unless enabled by control signals.

- These signals are generated in the control unit.

- There are two major types of control organization: hardwired control and micro programmed control.

A program consisting of the **memory unit of the computer** includes a series of instructions. The program is implemented on the computer by going through a cycle for each instruction.

In the basic computer, each instruction cycle includes the following procedures -

- It can fetch instruction from memory.

- It is used to decode the instruction.

- It can read the effective address from memory if the instruction has an indirect address.

- It can execute the instruction.

After the following four procedures are done, the control switches back to the first step and repeats the similar process for the next instruction. Therefore, the cycle continues until a **Halt** condition is met. The figure shows the phases contained in the instruction cycle.

#### Instruction Cycle

#### Fetch Cycle

The address instruction to be implemented is held at the program counter. The processor fetches the instruction from the memory that is pointed by the PC.

Next, the PC is incremented to display the address of the next instruction. This instruction is loaded onto the instruction register. The processor reads the instruction and executes the important procedures.

#### **Execute Cycle**

The data transfer for implementation takes place in two methods are as follows -

- **Processor-memory** The data sent from the processor to memory or from memory to processor.

- **Processor-Input/Output** The data can be transferred to or from a peripheral device by the transfer between a processor and an I/O device.

In the execute cycle, the processor implements the important operations on the information, and consistently the control calls for the modification in the sequence of data implementation. These two methods associate and complete the execute cycle.

#### Memory Reference Instructions:

**Memory Reference Instructions** are instructions that involve accessing **main memory** for either fetching operands or storing results, typically using an **address field** in the instruction.

There are seven memory reference instructions which are as follows &

#### AND

The AND instruction implements the AND logic operation on the bit collection from the register and the memory word that is determined by the effective address. The result of this operation is moved back to the register.

#### ADD

The ADD instruction adds the content of the memory word that is denoted by the effective address to the value of the register.

#### LDA

The LDA instruction shares the memory word denoted by the effective address to the register.

#### STA

STA saves the content of the register into the memory word that is defined by the effective address. The output is next used to the common bus and the data input is linked to the bus. It needed only one micro-operation.

#### BUN

The Branch Unconditionally (BUN) instruction can send the instruction that is determined by the effective address. They understand that the address of the next instruction to be performed is held by the PC and it should be incremented by one to receive the address of the next instruction in the sequence. If the control needs to implement multiple instructions that are not next in the sequence, it can execute the BUN instruction.

#### BSA

BSA stands for Branch and Save return Address. These instructions can branch a part of the program (known as subroutine or procedure). When this instruction is performed, BSA will store the address of the next instruction from the PC into a memory location that is determined by the effective address.

#### ISZ

The Increment if Zero (ISZ) instruction increments the word determined by effective address. If the incremented cost is zero, thus PC is incremented by 1. A negative value is saved in the memory word through the programmer. It can influence the zero value after getting incremented repeatedly. Thus, the PC is incremented and the next instruction is skipped.

#### UNIT - II

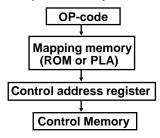

Micro programmed Control: Control memory, Address sequencing, micro program example, design of control unit.

**Central Processing Unit**: General Register Organization, Instruction Formats, Addressing modes, Data Transfer and Manipulation, Program Control.

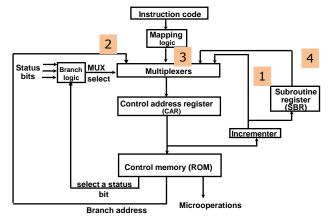

A control memory is a part of the control unit. Any computer that involves micro programmed control consists of two memories. They are the main memory and the control memory. Programs are usually stored in the main memory by the users. Whenever the programs change, the data is also modified in the main memory. They consist of machine instructions and data.

The control memory consists of micro programs that are fixed and cannot be modified frequently. They contain microinstructions that specify the internal control signals required to execute register micro-operations.

The machine instructions generate a chain of microinstructions in the control memory. Their function is to generate micro-operations that can fetch instructions from the main memory, compute the effective address, execute the operation, and return control to fetch phase and continue the cycle.

Here, the control is presumed to be a Read-Only Memory (ROM), where all the control information is stored permanently. ROM provides the address of the microinstruction. The other register, that is, the control data register stores the microinstruction that is read from the memory. It consists of a control word that holds one or more micro-operations for the data processor.

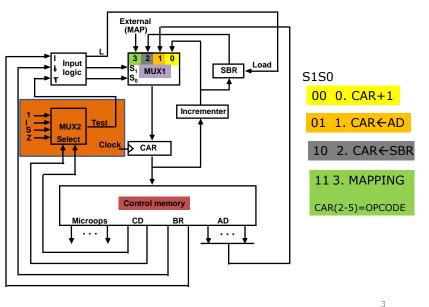

The next address must be computed once this operation is completed. It is computed in the next address generator. Then, it is sent to the control address register to be read. The next address generator is also known as the microprogram sequencer. Based on the inputs to a sequencer, it determines the address of the next microinstruction. The microinstructions can be specified in several ways. The main functions of a microprogram sequencer are as follows -

- It can increment the control register by one.

- It can load the address from the control memory to the control address register.

- It can transfer an external address or load an initial address to begin the start operation.

The data register is also known as the pipeline register. It allows two operations to be performed at a time. It allows performing the micro-operation specified by the control word and also the generation of the next microinstruction.

A dual-phase clock is required to be applied to the address register and the data register. It is possible to apply a single-phase clock to the address register and work without the control data register.

The main advantage of using a microprogrammed control is that, if the hardware configuration is established once, no further changes can be done. However, if a different control sequence is to be implemented, a new set of microinstructions for the system must be developed.

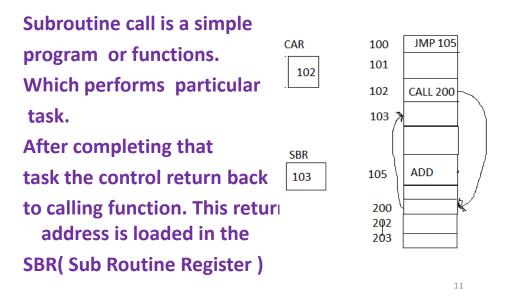

#### The address sequencing can be done in 4 ways.

1. Incrementing of the control address register.

2. Unconditional branch or conditional branch, depending on status bit conditions.

3. A mapping process from the bits of the instruction to an address for control memory.

#### 4. A facility for subroutine call and return.

13. Explain the role of microprogram Example ?

A micro program is a collection of microinstructions that tells a microprocessor how to perform operations. Micro programs are stored in control memories and can be used to customize and enhance the functionality of a CPU.

- In micro programming we have 5 sub topics

- 1) Computer Configuration

- 2) Micro Instruction format

- 3) Symbolic Micro instruction

- 4) Symbolic Micro Program5) Binary Micro program

#### MICROPROGRAM EXAMPLE

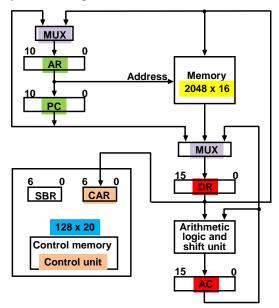

**Computer Configuration**

This contains two memories Units

- 1. Main Memory

- 2. Control Memory

Main Memory: This is used to store instructions and data. The capacity of Main Memory is 2048 x 16.

- It contains 2048 words , each word size is of 16 bits each.

- 11 bits are required to identify Address of each location.

Control Memory: used to store Micro program which is nothing but sequence of instructions.

The capacity of Main Memory is 128 x 20. each word is 20 bits and 07 bits are required to identify address of each location

- Control Memory is associated with CAR and SBR.

- CAR: Control Address Register : It provides the address of the micro instructions which are present in the control memory. The size of CAR is 7 bits.

- SBR : Sub Routine Register : when ever a subroutine called in the program the control transfers from main program to sub routine program, once those instructions are completed the control come back to the address which is specified by SBR. SBR contains return address.

- Here we have two multiplexers

- MUX -1 have two inputs from PC and DR and one output which goes to AR.

- MUX -2 have three inputs from PC , DR and main memory one output which goes to DR.

- Among these 4 registers two registers are associated for address( AR & PC), two registers are associated for data( DR & AC)

- AR-Address Register: It provides the address of the instructions that are stored in main memory. 11 bits. It is receiving information from Pc as well as DR through MUX-1

- PC: Program Counter always points the next instruction to be fetched. 11 bits. It is receiving information only from AR.

DR: Data Register contains the data. 16 bits. It is receiving information from AC, DR and main memory through MUX-2

8

Q

10

- AC: Accumulator : It contains the operands and the result. 16 bits. It is receiving information only from ALU.

- ALU is receiving information only from DR.

- Among these 4 registers two registers are associated for address( AR & PC), two registers are associated for data( DR & AC)

Main Memory Operations:

- Read Operation: If we want to perform read information from particular location which is present in main memory. We required address that provided by AR go to that location from that location read the data and send to the DR.

- Write Operation: DR provides data . That data to be write in memory location specified by the AR.

- Micro programmed unit provides control signals

#### MACHINE INSTRUCTION FORMAT

# Microinstruction Format

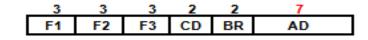

F1, F2, F3: Microoperation CD: Condition for branching BR: Branch field AD: Address field

11

#### MICROINSTRUCTION FIELD DESCRIPTIONS - F1, F2, F3

| F | F1  | Microoperation          | Symbol |  | F2  | Microoperation              | Symbol |

|---|-----|-------------------------|--------|--|-----|-----------------------------|--------|

| ( | 000 | None                    | NOP    |  | 000 | None                        | NOP    |

| C | 001 | $AC \leftarrow AC + DR$ | ADD    |  | 001 | AC $\leftarrow$ AC - DR     | SUB    |

| 0 | 010 | AC ← 0                  | CLRAC  |  | 010 | $AC \leftarrow AC \lor DR$  | OR     |

| C | 011 | AC $\leftarrow$ AC + 1  | INCAC  |  | 011 | $AC \leftarrow AC \land DR$ | AND    |

| 1 | 100 | AC ← DR                 | DRTAC  |  | 100 | $DR \leftarrow M[AR]$       | READ   |

| 1 | 101 | AR ← DR(0-10)           | DRTAR  |  | 101 | DR ← AC                     | ACTDR  |

| 1 | 110 | AR ← PC                 | PCTAR  |  | 110 | DR ← DR + 1                 | INCDR  |

| 1 | 111 | M[AR] ← DR              | WRITE  |  | 111 | DR(0-10) ← PC               | PCTDR  |

DRTAR

READ, INCPC

PCTAR

| F3  | Microoperation               | Symbol |

|-----|------------------------------|--------|

| 000 | None                         | NOP    |

| 001 | $AC \leftarrow AC \oplus DR$ | XOR    |

| 010 | AC ← AC'                     | COM    |

| 011 | AC $\leftarrow$ shI AC       | SHL    |

| 100 | AC ← shr AC                  | SHR    |

| 101 | $PC \leftarrow PC + 1$       | INCPC  |

| 110 | PC ← AR                      | ARTPC  |

| 111 | Reserved                     |        |

|     |                              |        |

12

#### MICROINSTRUCTION FIELD DESCRIPTIONS - CD, BR

| CD | Condition  | Symbol | Comments             |

|----|------------|--------|----------------------|

| 00 | Always = 1 | U      | Unconditional branch |

| 01 | DR(15)     | 1      | Indirect address bit |

| 10 | AC(15)     | s      | Sign bit of AC       |

| 11 | AC = 0     | l z    | Zero value in AC     |

| BR | Symbol | Function                                 |  |

|----|--------|------------------------------------------|--|

| 00 | JMP    | CAR ← AD if condition = 1                |  |

|    |        | CAR ← CAR + 1 if condition = 0           |  |

| 01 | CALL   | CAR ← AD, SBR ← CAR + 1 if condition = 1 |  |

|    |        | CAR ← CAR + 1 if condition = 0           |  |

| 10 | RET    | CAR ← SBR (Return from subroutine)       |  |

| 11 | MAP    | CAR(2-5) ← DR(11-14), CAR(0,1,6) ← 0     |  |

Microprogram sequencer in generating next address for control memory?

The basic components of a microprogrammed control unit are the control memory and the circuits that select the next address.

The address selection part is called a microprogram sequencer.

The purpose of a microprogram sequencer is to present an address to the control memory so that a microinstruction may be read and executed.

The next-address logic of the sequencer determines the specific address source to be loaded into the control address register.

The block diagram of the microprogram sequencer is shown in below figure.

#### MICROPROGRAM PROGRAMMED CONTROL

#### MICRO PROGRAM EXAMPLE

- Microprogrammed Control Unit : Microprogrammed Control Unit produces control signals by using microinstructions.

- Micro program :

- A program is a set of instructions. An instruction requires a set of microoperations.

- Micro-operations are performed using control signals.Here, these control signals are generated using micro-instructions.This means every instruction requires a set of micro-instructions

- A set of micro-instructions are called micro-program.

- Microprograms for all instructions are stored in a small memory called control memory.

The control memory is present inside the processor.

Consider an instruction that is fetched from the main memory into the instruction Register (IR). The processor uses its unique opcode to identify the address of the first micro-instruction. That address is loaded into CMAR (Control Memory Address Register). This address is decoded to decide the corresponding memory instruction from the control Memory.

4

5

Micro-instructions will only have a control field. The control field Indicates the control signals to be generated. Most micro-instructions will not have an address field. Usually PC will simply get incremented after every micro-instruction.

- This is as long as the micro-program is executing sequentially. If there is a branch micro-instruction only then there will be an address filed.

- If the branch is unconditional, the branch address will be directly loaded into CMAR. For conditional branches, the branch condition will check the appropriate flag.

- This is done using a MUX which has all flag inputs. If the condition is true, then the mux will inform CMAR to load the branch address.

- If the condition is false CMAR will simply get incremented. The control memory is usually implemented using flash ROM as it is non-volatile.

#### **MICROINSTRUCTION FIELD DESCRIPTIONS - CD, BR**

| CD | Condition  | Symbol | Comments             |

|----|------------|--------|----------------------|

| 00 | Always = 1 | U      | Unconditional branch |

| 01 | DR(15)     | 1      | Indirect address bit |

| 10 | AC(15)     | s      | Sign bit of AC       |

| 11 | AC = 0     | z      | Zero value in AC     |

| BR | Symbol | Function                                 |  |

|----|--------|------------------------------------------|--|

| 00 | JMP    | CAR ← AD if condition = 1                |  |

|    |        | CAR ← CAR + 1 if condition = 0           |  |

| 01 | CALL   | CAR ← AD, SBR ← CAR + 1 if condition = 1 |  |

|    |        | CAR ← CAR + 1 if condition = 0           |  |

| 10 | RET    | CAR ← SBR (Return from subroutine)       |  |

| 11 | MAP    | CAR(2-5) ← DR(11-14), CAR(0,1,6) ← 0     |  |

0XXXX00 0001000

#### ADDRESS SEQUENCING

- Incrementing of the control address register An initial address is loaded into the control address register when power is turned on in the computer (CAR=100)

- This address is usually the address of the first

- microinstruction that activates the instruction fetch routine.

- At the end of the fetch routine, the content of the CAR is incremented to fetch the next instruction in sequence.

- Incrementor increments the content of CAR by 1(CAR=101). This is loaded in to CAR through the multiplexer.

5

6

Unconditional branch or conditional branch, depending on status bit conditions.

- Without checking the any condition we are transferring the program control from one location to another location. That branch address is specified within the instruction.

- Example: Branch Address is 105 specified in the instruction.

# conditional branch, depending on status bit conditions

- In this operation we need to check the condition (Zero flag, Sign Flag, Carry Flag)of Branch Logic (BL)

- If BL= 1 :we need to go to that particular location

- If BL= 0: simply move forward and increment the CAR.

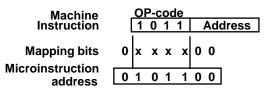

# A mapping process from the bits of the instruction to an address for control memory.

- Conversion from 4 bit opcode into 7 bit address in control memory where the data is located is referred to as a mapping process.

- A mapping procedure is a rule that transforms the instruction code into a control memory address.

#### MAPPING OF INSTRUCTIONS TO MICROROUTINES

Mapping from the OP-code of an instruction to the address of the Microinstruction which is the starting microinstruction of its execution microprogram

Mapping function implemented by ROM or PLA

10

## A facility for Subroutine Call and Return.

Here multiplexer  $(4 \times 1)$  getting from 4 inputs and produces one output. This output which is the address of the operand is loaded in CAR. Here Car operated by Clock .

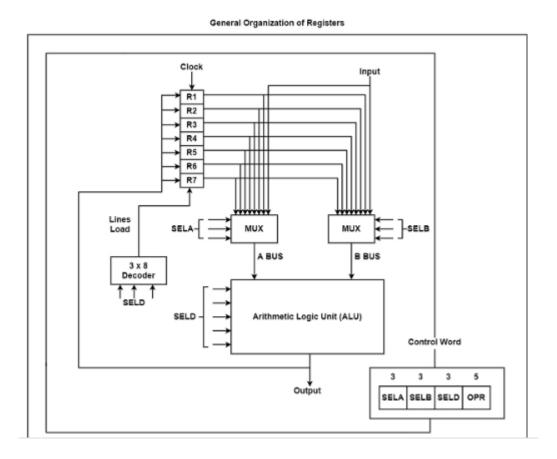

Registers implement two important functions in the CPU operation are as follows -

- It can support a temporary storage location for data. This supports the directly implementing programs to have fast access to the data if required.

- It can save the status of the CPU and data about the directly implementing program

If a CPU includes some registers, therefore a common bus can link these registers. A general organization of seven CPU registers is displayed in the figure.

# The CPU bus system is managed by the control unit. The control unit explicit the data flow through the <u>ALU</u> by choosing the function of the ALU and components of the system.

Consider R1  $\leftarrow$  R2 + R3, the following are the functions implemented within the CPU –

MUX A Selector (SELA) – It can place R2 into bus A.

MUX B Selector (SELB) – It can place R3 into bus B.

ALU Operation Selector (OPR) – It can select the arithmetic addition (ADD).

**Decoder Destination Selector (SELD)** – It can transfers the result into R1.

The multiplexers of 3-state gates are performed with the buses. The state of 14 binary selection inputs determines the control word. The 14-bit control word defines a micro-operation.

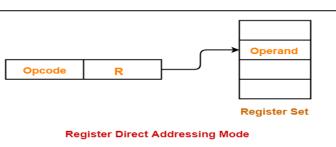

Addressing modes with numerical example.

**Types of Addressing Modes**

- 1. Implied Mode

- 2.Immediate Mode

- 3.RegisterAddressing Mode

- 4. Register Indirect Mode

- 5. Direct Addressing Mode

- 6. Indirect Addressing Mode

- 7. Relative Addressing Mode

- 8. Indexed Addressing Mode

- 9. Base Register Addressing Mode

- 10. Auto Increment Addressing Mode

- 11. Auto Decrement Addressing Mode

**1. Implied Mode:** Address of the operands are specified implicitly in the definition of the instruction. No need to specify address in the instruction EX:

- CMA (Complement Accumulator)

- CLA Clear Accumulator,

- INC Increment Accumulator

Zero address instructions in stack organization are Implied Mode instruction

#### Ex: PUSH A, PUSH B

2. Immediate Mode : The operand itself is specified explicitly in the definition of the instruction. The operand field contains operand rather than address field. Fast to acquire an operand.

EX:

- MOV A #10 # indicates that 10 is immediate value

- ADD 23,45

This addressing is used for initializing registers to a constant value

**3.**Register Addressing Mode : In this mode the operand is specified in the register. The name of the register is specified In the instruction

Advatages:

- -- Shorter address than the memory address

- -- Saving address field in the instruction

- -- Faster to acquire an operand than the memory addressing

EX: MOV A,B ADD R1,R2 R1=23 R2=45

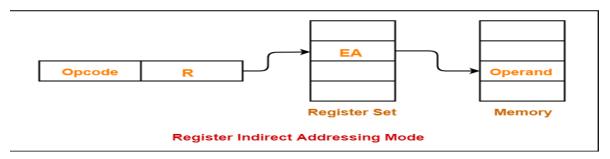

**4. Register Indirect Addressing Mode :** Instruction specifies a register which contains the memory address of the operand

- Ex:

- MOV A, [R0]

R0 contains the address of the operand in memory

go to that address in memory to fetch the data , that data is moved to A.

- When the address in the register is used to access memory, the value in the register is incremented or decremented by 1 Automatically

- R0 does nor contain data

R0 contains the address of the data where it is located

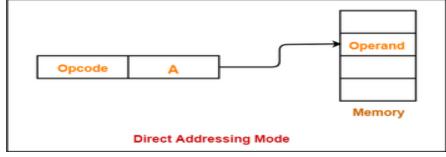

**5. Direct Address Mode** : Instruction specifies the memory address which can be used directly to the physical memory

EX:

MOV A , 2000

This instruction copy the data present in the location 2000 and move to register A.

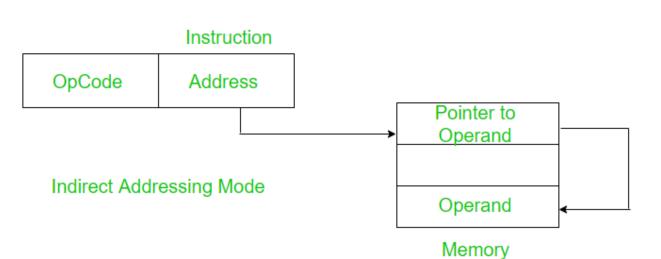

6. **Indirect Addressing Mode:** The address field of an instruction specifies the address of a memory location that contains the address of the operand.

EX: MOV A, [2000] let the content of 2000 is 3000 3000 is the address of the operand In address 3000 we can get the operand

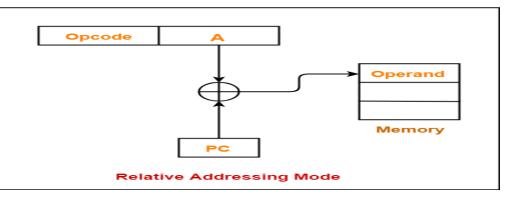

**7.Relative Addressing Modes:** The content of the program counter is added to the address part of the instruction in order to get the effective address of the operand.

Effective Address= Address of the operand

EA= PC+ Address present in the address part of the instruction.

Let PC contains 825

The address part of the Instruction contains = 24

The instruction at location 825 is read from the memory during fetch phase and program counter is incremented by 1 so present value in PC=826 then

The address of the operand = 826+24=850

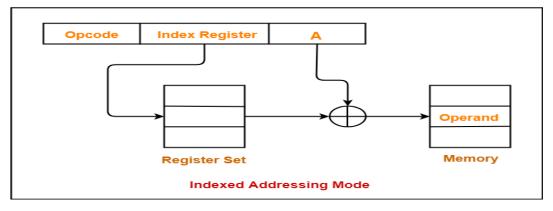

**8.Indexed Addressing Mode :**In this addressing mode the content of the index register is added to the address part of the instruction to obtain the address of the operand or Effective Address.

Index Register(IR) Is a special CPU register which contains the index value.

Effective Address=

Content of the Index Register + Address part of the instruction.

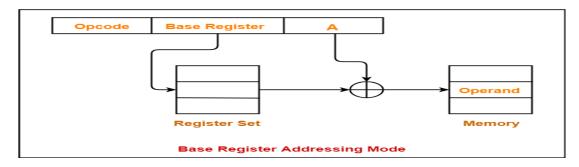

**9. Base Register Addressing Mode :** In this addressing mode the content of the Base Register is added to the address part of the instruction to obtain the address of the operand or Effective Address.

Effective Address = content of the Base Register + Address part of the instruction

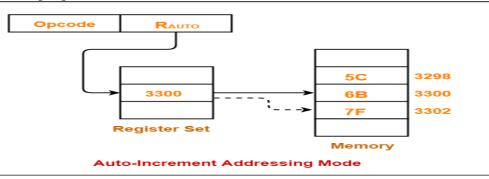

#### 10. Auto Increment Addressing Mode

In this addressing mode the Effective Address operand is the content of the register specified in the instruction. After accessing the operand the content of this register are incremented to the address of the next location.

#### EX:

MOV R1 [R0]+

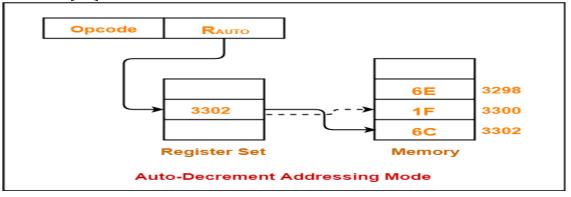

**11. Auto Decrement Addressing Mode :** In this addressing mode the Effective Address operand is the content of the register specified in the instruction. After accessing the operand the content of this register are decremented to the address of the next location. EX:

#### MOV R1 -[R0]

Instruction formats with suitable example

#### **INSTRUCTION FORMAT**

A Program is a Set of instructions that instruction are stored in the memory in particular format, that format is called instruction format.

This instruction format has 32 bit , 64 bit and 16 bit formats. Here we are using 16 bit format The bits of the instruction format divided into fields.

#### Instruction Format

- Mode field specifies the way the operand or the effective address is determined I = 0 → Direct Addressing Mode

- $I = 1 \rightarrow$  Indirect Addressing Mode

- OP-code field specifies the operation to be performed Examples of opcodes ADD: Adds two values SUB: Subtracts two values DIV: Divides two values

- Address field designates memory address(es) or a processor register(s)

The number of address fields in the instruction format depends on the internal organization of CPU

- Three-address Instructions

- Two-address Instructions

- One-address Instructions

- Zero-address Instructions

Example = (A + B) \* (C + D)

#### THREE ADDRESS INSTRUCTIONS

- Advantages:

- - Results in short programs

- Disadvantages:

- Instruction becomes long(many bits) to specify three addresses

- Program to evaluate X = (A + B) \* (C + D)

OPCODE ADDRESS FIELD1 ADD F2 ADD F 3

| ADD | R1, A, B  | $R1 \leftarrow M[A] + M[B]$ |

|-----|-----------|-----------------------------|

| ADD | R2,C,D    | $R2 \leftarrow M[C] + M[D]$ |

| MUL | X, R1, R2 | M[X] ← R1 * R2              |

1

1

#### **TWO ADDRESS INSTRUCTIONS**

• Program to evaluate X = (A + B) \* (C + D) :

| OPCODE                                 | ADDRESS<br>FIELD1                       | ADD F2            |                                                                                                                                            |  |

|----------------------------------------|-----------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| MOV<br>ADD<br>MOV<br>ADD<br>MUL<br>MOV | R1,<br>R1,<br>R2,<br>R2,<br>R1,<br>X, F | B<br>C<br>D<br>R2 | $R1 \leftarrow M[A]$ $R1 \leftarrow R1 + M[B]$ $R2 \leftarrow M[C]$ $R2 \leftarrow R2 + M[D]$ $R1 \leftarrow R1 * R2$ $M[X] \leftarrow R1$ |  |

Computers with two-address instructions are most common

#### **ONE-ADDRESS INSTRUCTIONS**

- One-Address Instructions

- - Use an implied AC register for all data manipulation

- - Program to evaluate X = (A + B) \* (C + D) :

OPCODE ADDRESS FIELD1

$$X = (A + B) * (C + D)$$

is

| LOAD  | A | AC←M[A]                   |

|-------|---|---------------------------|

| ADD   | В | $AC \leftarrow AC + M[B]$ |

| STORE | т | $M[T] \leftarrow AC$      |

| LOAD  | С | $AC \leftarrow M[C]$      |

| ADD   | D | $AC \leftarrow AC + M[D]$ |

| MUL   | т | AC←AC*M[T]                |

| STORE | Х | M[X] ← AC                 |

7

8

# **Zero-Address Instructions**

- - Can be found in a stack-organized computer

- - Program to evaluate X = (A + B) \* (C + D) :

| OPCOD | <b>=</b>                           |

|-------|------------------------------------|

|       |                                    |

| A     | TOS ← A                            |

| I B   | TOS ← B                            |

|       | $TOS \leftarrow (A + B)$           |

| I C   | TOS ← C                            |

| I D   | TOS←D                              |

|       | $TOS \leftarrow (C + D)$           |

|       | $TOS \leftarrow (C + D) * (A + B)$ |

| X     | M[X] ←TOS                          |

|       | I B<br>I C<br>I D                  |

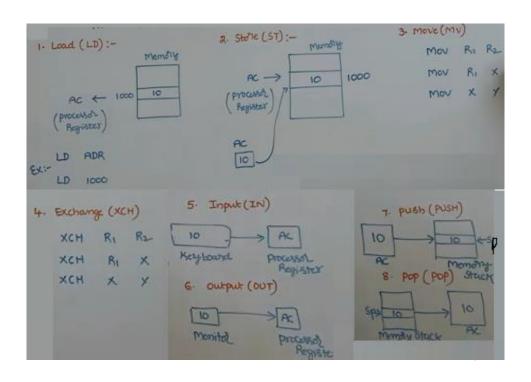

Data transfer, data manipulation and program control instructions.

# **COMPUTER INSTRUCTIONS**

- Basic computer instructions are commands given to a computer to perform specific tasks. These instructions are typically divided into three categories:

- Data Transfer Instructions: Move data between memory and registers (e.g., Load, Store).

- Data Manipulation Instructions : Perform math or logic operations (e.g., Add, Subtract, AND, OR).

- **Control Instructions**: Guide the flow of the program (e.g., Jump, Branch, Call).

| NAME         | MNEMONICS | DESCRIPTION                                                           |

|--------------|-----------|-----------------------------------------------------------------------|

| Load:        | LD        | Copies data from memory to a register                                 |

| Store:       | ST        | Transfers data from a register to memory.                             |

| Move         | MOV       | Transfers data from one register to another.                          |

| Exchan<br>ge | ХСН       | Exchange the data from one location to another                        |

| Input        | IN        | Provide data to a computer program or system. I                       |

| Output       | OUT       | Moves data from a memory address to an I/O port                       |

| Push         | PUSH      | Saves data to a stack in memory                                       |

| Рор          | РОР       | Retrieves data from a stack, or restores the status of an instruction |

#### DATA MANIPULATION INSTRUCTIONS

These instructions modify data to execute program

They are broadly categorized into three types:

- -Arithmetic instructions

- Logical and bit manipulation instructions

- Shift instructions

#### DATA MANIPULATION INSTRUCTIONS

#### Three Basic Types: Arithmetic instructions Logical and bit manipulation instructions Shift instructions

Arithmetic Instructions

| Name                   | Mnemonic |

|------------------------|----------|

| Increment              | INC      |

| Decrement              | DEC      |

| Add                    | ADD      |

| Subtract               | SUB      |

| Multiply               | MUL      |

| Divide                 | DIV      |

| Add with Carry         | ADDC     |

| Subtract with Borrow   | SUBB     |

| Negate(2's Complement) | NEG      |

Logical and Bit Manipulation Instructions

| Name              | Mnemonic |

|-------------------|----------|

| Clear             | CLR      |

| Complement        | COM      |

| AND               | AND      |

| OR                | OR       |

| Exclusive-OR      | XOR      |

| Clear carry       | CLRC     |

| Set carry         | SETC     |

| Complement carry  | y COMC   |

| Enable interrupt  | EI       |

| Disable interrupt | DI       |

| Shift Instructions      |          |  |

|-------------------------|----------|--|

| Name                    | Mnemonic |  |

| Logical shift right     | SHR      |  |

| Logical shift left      | SHL      |  |

| Arithmetic shift right  | SHRA     |  |

| Arithmetic shift left   | SHLA     |  |

| Rotate right            | ROR      |  |

| Rotate left             | ROL      |  |

| Rotate right thru carry | RORC     |  |

| Rotate left thru carry  | ROLC     |  |

6

Program Control Instructions are the machine code instructions which are used to control the flow of execution of instructions in the processor domain. These are important in instilling on the processor how to execute a certain task, access different programs and control the decision making on the basis of some conditions. They are commonly used in <u>assembly language</u> and generated by high level language which is compiled into machine code form to enable the processor act in the desired manner.

## **Types of Program Control Instructions**

#### **1.** Compare Instruction

Compare instruction is specifically provided, which is similar to a subtract instruction except the result is not stored anywhere, but flags are set according to the result. *Example: CMP R1*, *R2*;

#### 2. Unconditional Branch Instruction

It causes an unconditional change of execution sequence to a new location. *Example: JUMP L2 Mov R3, R1 goto L2*

#### **3.** Conditional Branch Instruction

A conditional branch instruction is used to examine the values stored in the condition code register to determine whether the specific condition exists and to branch if it does.

Example: Assembly Code :

BE R1, R2, L1 Compiler allocates R1 for x and R2 for y

*High Level Code: if* (x==y) *goto L1;*

# 4. Subroutines

A subroutine is a program fragment that lives in user space, performs a well-defined task. It is invoked by another user program and returns control to the calling program when finished.

**Example:** CALL and RET

# **5. Halting Instructions**

- **NOP Instruction** NOP is no operation. It cause no change in the processor state other than an advancement of the program counter. It can be used to synchronize timing.

- **HALT** It brings the processor to an orderly halt, remaining in an idle state until restarted by interrupt, trace, reset or external action.

# **6. Interrupt Instructions**

Interrupt is a mechanism by which an I/O or an instruction can suspend the normal execution of processor and get itself serviced.

- **RESET** It reset the processor. This may include any or all setting registers to an initial value or setting program counter to standard starting location.

- **TRAP** It is non-maskable edge and level triggered interrupt. TRAP has the highest priority and vectored interrupt.

- **INTR** It is level triggered and maskable interrupt. It has the lowest priority. It can be disabled by resetting the processor.

# **Advantages of Program Control Instructions**

• Efficient Control Flow: Program Control Instructions provide the processor with the means to decide the order of instructions. This means that branching can be efficiently made which is important for complicated

# UNIT - III

**Data Representation**: Data types, Complements, Fixed Point Representation, Floating Point Representation.

**Computer Arithmetic:** Addition and subtraction, multiplication Algorithms, Division Algorithms, Floating – point Arithmetic operations. Decimal Arithmetic unit, Decimal Arithmetic operations

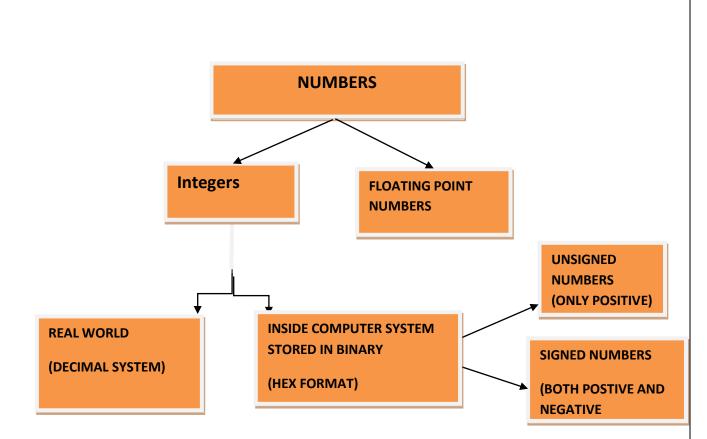

## **Data Representation:**

- Data Representation refers to the form in which data is stored, processed, and transmitted.

- In computer organization, data refers to the symbols that are used to represent events, people, things and ideas.

Data can be anything like a number, a name, notes in a musical composition, or the color in a photograph. Data representation can be referred to as the form in which we stored the data, processed it and transmitted it. In order to store the data in digital format, we can use any device like computers, smartp hones, and iPads. Electronic circuitry is used to handle the stored data.

The Number Systems used in computers are

- Binary number system

- Octal number system

- Decimal number system

- Hexadecimal number system

- Binary Coded decimal number system(BCD)

## **Binary number system**

- It has only two digits '0' and '1' so its base is 2. Each digit is called a bit.

- A group of four bits (1101) is called a nibble a

- Group of eight bits (11001010) is called a byte. The position of each digit in a binary number represents a specific power of the base (2) of the number system.

| Decimal<br>Number | Binary<br>Number |

|-------------------|------------------|

| 0                 | 0000             |

| 1                 | 0001             |

| 2                 | 0010             |

| 3                 | 0011             |

| 4                 | 0100             |

| 5                 | 0101             |

| 6                 | 0110             |

| 7                 | 0111             |

| 8                 | 1000             |

| 9                 | 1001             |

| 10                | 1010             |

| 11                | 1011             |

# Octal number system

• It has eight digits (0, 1, 2, 3, 4, 5, 6, 7) so its base is 8. Each digit in an octal number represents a specific power of its base (8). The three binary digits can be represented with a single octal digit.

| Decimal Number | Octal Number |

|----------------|--------------|

| 0              | 0            |

| 1              | 1            |

| 2              | 2            |

| 3              | 3            |

| 4              | 4            |

| 5              | 5            |

| 6              | 6            |

| 7              | 7            |

| 8              | 10           |

| 9              | 11           |

| 10             | 12           |

| 11             | 13           |

| 12             | 14           |

## **Decimal number system**

- This number system has ten digits (0, 1, 2, 3, 4, 5, 6, 7, 8, 9) so its base is 10.

- In this number system, the maximum value of a digit is 9 and the minimum value of a digit is 0.

- The position of each digit in decimal number represents a specific power of the base (10) of the number system. This number system is widely used in our day to day life.

- It can represent any numeric value.

Hexadecimal number system:

- This number system has 16 digits that ranges from 0 to 9 and A to F. So, its base is 16.

- The A to F alphabets represent 10 to 15 decimal numbers.

- The position of each digit in a hexadecimal number represents a specific power of base (16) of the number system.

- It is also known as alphanumeric number system as it uses both numeric digits and alphabets

| Decimal Number | Hexa Decimal Number |

|----------------|---------------------|

| 0              | 0                   |

| 1              | 1                   |

| 2              | 2                   |

| 3              | 3                   |

| 4              | 4                   |

| 5              | 5                   |

| 6              | 6                   |

| 7              | 7                   |

| 8  | 8 |

|----|---|

| 9  | 9 |

| 10 | Α |

| 11 | В |

| 12 | С |

## **Binary Coded Decimal Number.:**

BCD stands for Binary Coded Decimal Number. In BCD code, each digit of the decimal number is represented as its equivalent binary number. So, the LSB and MSB of the decimal numbers are represented as its binary numbers.

Truth Table for Binary Coded Decimal

| DECIMAL NUMBER | BCD  |           |               |               |               |

|----------------|------|-----------|---------------|---------------|---------------|

| 0              | 0000 | 9<br>     | <b>О</b><br>П | <b>8</b><br>几 | <b>7</b><br>∬ |

| 1              | 0001 | ∛<br>1001 | V<br>0000     | V<br>1000     | V<br>0111     |

| 2              | 0010 | 1001      | 0000          | 1000          | 0111          |

| 3              | 0011 |           |               |               |               |

# **NUMBER REPRESENTATION:**

#### **UNSIGNED INTEGERS**

These are binary numbers that are always assumed to be positive.Here all available bits of the number are used to represent the magnitude of the number.No bits are used to indicate itssign, hence they are called unsigned numbers. E.g.: Roll Numbers, Memory addresses etc

#### **SIGNED INTEGERS**

These are binary numbers that can be either positive or negative. The MSB of the number indicates whether it is positive or negative. If **MSB is 0 then the number is Positive**. If **MSB is 1 then the number is Negative**. Negative numbers are always stored in 2's complement form.

Three systems are used forrepresenting such numbers:

- Signed magnitude

- 1's-complement

- 2's-complement

In all three systems, the leftmost bit is 0 for positive numbers and 1 for negative numbers.Positive values have identical representations in all systems, but negative values have different representations.

In the **signed magnitude system**, negative values are represented by changing the most significant bit from 0 to 1. For example, +5 is represented by 0101, and -5 is represented by 1101.

In **1's-complement representation**, negative values are obtained by complementing eachbit of the corresponding positive number. Thus, the representation for -3 is obtained by complementing each bit in the vector 0011 to yield 1100. The same operation, bitcomplementing, is done to convert a negative number to the corresponding positive value.

| В                      | •                  | Values represented |                |

|------------------------|--------------------|--------------------|----------------|

| $b_{3}b_{2}b_{1}b_{0}$ | Sign and magnitude | 1's complement     | 2's complement |

| 0 1 1 1                | + 7                | + 7                | + 7            |

| 0 1 1 0                | + 6                | + 6                | + 6            |

| 0 1 0 1                | + 5                | + 5                | + 5            |

| 0100                   | + 4                | + 4                | + 4            |

| 0011                   | + 3                | + 3                | + 3            |

| 0010                   | + 2                | + 2                | + 2            |

| 0001                   | + 1                | + 1                | + 1            |

| 0000                   | + 0                | + 0                | + 0            |

| 1 0 0 0                | - 0                | - 7                | - 8            |

| 1001                   | - 1                | - 6                | - 7            |

| $1 \ 0 \ 1 \ 0$        | - 2                | - 5                | - 6            |

| $1 \ 0 \ 1 \ 1$        | - 3                | - 4                | - 5            |

| $1 \ 1 \ 0 \ 0$        | - 4                | - 3                | - 4            |

| 1 1 0 1                | - 5                | - 2                | - 3            |

| $1 \ 1 \ 1 \ 0$        | - 6                | - 1                | - 2            |

| $1 \ 1 \ 1 \ 1$        | -7                 | - 0                | - 1            |

## Fig: Binary signed number Representations

**Two's complement gives a unique representation for zero.** Any other system gives a separate representation for +0 and for -0. This is absurd. In two's complement system, -(x) is stored as two's complement of (x). Applying the same rule for 0, -(0) should be stored as two's complement of 0. 0 is stored as 000. So -(0) should be stored as two's complement of 000, which again is 000. Hence two's complement gives a unique representation for 0.**It produces an additional number on the negative side.** As two's complement system produces a unique combination for 0, it has a spare combination '1000' in the above case, and can be used to represent -(8).

| 3 BIT INTEGER                      |           |  |

|------------------------------------|-----------|--|

| $2^3 = 8$ therefore 8 combinations |           |  |

| Unsigned Signed                    |           |  |

| 0 7                                | -41 0 1 3 |  |

| 4 BIT INTEGER                                 |           |  |

|-----------------------------------------------|-----------|--|

| 2 <sup>4</sup> = 16 therefore 16 combinations |           |  |

| Unsigned Signed                               |           |  |

| 0 15                                          | -81 0 1 7 |  |

## **Fixed and Floating point Representations:**

There are two major approaches to store real numbers (i.e., numbers withfractional component) in modern computing. These are

- (i) Fixed Point Notation and

- (ii) Floating Point Notation.

**Fixed Point Notation:** In **fixed point notation**, there are a fixed number of digits after the decimal point, whereas **floating point number** allows for avarying number of digits after the decimal point.

This representation has fixed number of bits for integer part and for fractional part. For example, if given fixed-point representation is IIII.FFFF, then you can store minimum value is 0000.0001 and maximum value is 9999.9999. There are three parts of a fixed-point number representation: the sign field, integer field, and fractional field.

| Unsigned fixed point |      | Integer | Fraction |

|----------------------|------|---------|----------|

| Signed fixed point   | Sign | Integer | Fraction |

Assume number is using 32-bit format which reserve 1 bit for the sign, 15 bits for the integer part and 16 bits for the fractional part. Then, -43.625 is represented as following:

| 1           | 000000000101011 | 1010000000000000 |

|-------------|-----------------|------------------|

| Sign<br>bit | Integer part    | Fractional part  |

Where, 0 is used to represent + and 1 is used to represent -. 000000000101011 is 15bit binary value for decimal 43 and 10100000000000 is 16-bit binary value for fractional 0.625. The advantage of using a fixed-point representation is performance and disadvantage is relatively limited range of values that they can represent. So, it is usually inadequate for numerical analysis as it does not allow enough numbers and accuracy. A number whose representation exceeds 32 bits would have to be stored inexactly.

Floating Point Representation:

In some numbers, which have a fractional part, the position of the decimal point is not fixed as the number of bits before (or after) the decimal point may vary. **Eg: 0010.01001, 0.0001101, -1001001.01** etc. the position of the decimal point is not fixed, instead it''floats'' in the number.Such numbers are called Floating Point Numbers. Floating Point Numbers are stored in a "Normalized" form.

# **NORMALIZATION OF A FLOATING POINTNUMBER:**

Normalization is the process of shifting the point, left or right, so that there is only one non-zero digit to the left of the point.

01010.01 (-1) $\boldsymbol{0} \ge 1.01001 \ge 2^3$

11111.01 (-1) $\boldsymbol{0} \ge 1.111101 \ge 2^4$

-10.01 (-1) $\boldsymbol{1} \ge 1.001 \ge 2^1$

A normalized form of a number is:

-1<sup>s</sup> x1.MX2<sup>E</sup> Where: S = Sign, M = Mantissa and E = Exponent.

As Normalized numbers are of the 1.M format, the "1" is not actually stored, it is instead assumed. Also the Exponent is stored in the biased form by adding an appropriate bias value to it so that -ve exponents can be easily represented.

## Advantages of Normalization.

1. Storing all numbers in a standard for makes calculations easier and faster.

2. By not storing the 1 (of 1.M format) for a number, considerable storage space is saved.

3. The **exponent** is **biased** so there is **no need** for **storing** its **sign bit** (as the biased exponent cannot be -ve).

## SHORT REAL FORMAT / SINGLE PRECISION FORMAT / IEEE 754: 32 BIT FORMAT:

| S   | Biased Exponent         | Mantissa  |

|-----|-------------------------|-----------|

| (1) | (8)<br>Bias value = 127 | (23 bits) |

- 1. **32 bits** are used to store the **number**.

- 2. 23 bits are used for the Mantissa.

- 3. 8 bits are used for the Biased Exponent.

- 4. 1 bit used for the Sign of the number.

- **5.** The **Bias** value is  $(127)_{10}$ .

# Range: $+1 \times 10^{-38}$ to $+3 \times 10^{38}$

## LONG REAL FORMAT / DOUBLE PRECISION FORMAT / IEEE 754: 64 BIT FORMAT

- **<u>1.</u>** 64 bits are used to store the number.

- 2. 52 bits are used for the Mantissa.

- 3. 11 bits are used for the Biased Exponent.

- **<u>4.</u>** 1 bit used for the Sign of the number.

- **<u>5.</u>** The **Bias** value is (**1023**)<sub>10</sub>.

- **6.** The range is  $+10^{-308}$  to  $+10^{308}$  approximately.

| S     | <b>Biased Exponent</b> |       | Mantissa |

|-------|------------------------|-------|----------|

| 1 bit | 11-bits                | (Bias | 52-bits  |

|       | value:1023)            |       |          |

#### **Extreme cases of floating point numbers:**

Floating point numbers are represented in IEEE formats.Consider IEEE 754 32-bit format also called Single Precision format or Short real format.

#### **Overflow:**

For a value, 1.0 the normalized form will be

$(-1)^0 \ge 1.0 \ge 2^0$

Herethe True Exponent is 0.

| If: | TE = 0,   | BE = 127 | Representation | = | 0111 | 1111 |

|-----|-----------|----------|----------------|---|------|------|

| If: | TE = 1,   | BE = 128 | Representation | = | 1000 | 0000 |

| If: | TE = 2,   | BE = 129 | Representation | = | 1000 | 0000 |

|     |           |          |                |   |      |      |

| If: | TE = 127, | BE = 254 | Representation | = | 1111 | 1110 |

| If: | TE = 128, | BE = 255 | Representation | = | 1111 | 1111 |

| If: | TE = 129, | BE = 255 | Representation | = | 1111 | 1111 |

| If: | TE = 130, | BE = 255 | Representation | = | 1111 | 1111 |

|     |           |          |                |   |      |      |

This is because the 8-bit biased exponent cannot hold a value more than 255.Hence, all cases where the TE = 128 or more, the *BE will be represented as 1111 1111.This indicates as exception (error) called OVERFLOW. The number is called NaN (Not a Number)*.It is identified by Exponent being all 1s (1111 1111).Here, the Mantissa can be anything!The **Extreme case of NaN is Infinity**.It is also an OVERFLOW and hence the Exponent will be 1111 1111.To differentiate Infinity from NaN, the Mantissa in infinity is 0000 0000.Hence **Infinity is identified as Exponent all 1s and Mantissa all 0s.**

Suppose the number is 0.1.It will be normalized as

$(-1)^0 \ge 1.0 \ge 2^{-1}$

The true exponent here is -1.

|     | TE = -1,<br>TE = -2,     | BE = 126<br>BE = 125 | Representation :                  |        |      |

|-----|--------------------------|----------------------|-----------------------------------|--------|------|

| ··· | IE2,                     | BE - 125             | Representation :                  |        |      |

|     | TE = -126,<br>TE = -127, |                      | Representation = Representation = |        |      |

|     | TE = -128,               |                      | Representation :                  |        |      |

| If: | TE = -129,               | BE = 0               | Representation :                  | = 0000 | 0000 |

**Underflow:** All cases where the TE = -127 or less, the BE will be represented as 0000 0000. This indicates as exception (error) called UNDERFLOW.

The number is called De-Normal Number.It is identified by Exponent being all 0s (0000 0000).Here, the Mantissa can be anything.The **Extreme case of De-Normal Number is Zero.**

It is also an UNDERFLOW and hence the Exponent will be 0000 0000.To differentiate Zero from De-Normal Number, the Mantissa in Zero is 0000 0000.Hence **Zero is identified as Exponent all 0s and Mantissa all 0s**.This means Zero is represented as all 0s.

## **Example:**Convert 2A3BH into Short Real format.

```

Soln: Converting the number into binary we get:

0010\ 1010\ 0011\ 1011

Normalizing the number we get:

(-1)^0 \mathbf{x}\ 1.0101000111011\ \mathbf{x}\ 2^{13}

Here S = 0; M = 0101000111011; True Exponent = 13.

Bias value for Short Real format is 127:

Biased Exponent (BE) = True Exponent + Bias

= 13 + 127

= 140.

Converting the Biased exponent into binary we get:

Biased Exponent (BE) = (1000\ 1100)

```

#### **Representing in the required format we get:**

S Biased Exp Mantissa (1) (8) (23)

## **Computer Arithmetic**

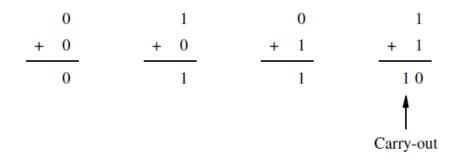

#### **Integer Addition:**

**Addition of Unsigned Integers:** Addition of 1-bit numbers is illustrated below. The sum of 1 and 1 is the 2-bit vector 10, which represents the value 2. We say that the sum is 0 and the carry-out is 1. In order to add multiple-bit numbers, We add bit pairs starting from the low-order (right)

end of the bit vectors, propagating carries toward the high-order (left) end. The carry-out from a bit pair becomes the carry-in to the next bit pair to the left. The carry-in must be added to a bit pair in generating the sum and carry-out at that position. For example, if both bits of a pair are 1 and the carry-in is 1, then the sum is 1 and the carry-out is 1, which represents the value 3.

#### Fig: Addition of 1-bit Numbers

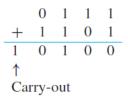

## Addition and Subtraction of Signed Integers:

To add two numbers, add their n-bit representations, ignoring the carry-out bit from the most significant bit (MSB) position. The sum will be the algebraically correct value in2's-complement representation if the actual result is in the range– $(2^{n-1})$  through+ $2^{n-1}$ – 1.

To subtract two numbers X and Y, that is, to perform X - Y, form the 2's-complement of Y, then add it to X using the add rule. Again, the result will be the

algebraically correct value in 2's-complement representation if the actual result is in the range  $-(2^{n-1})$  through  $+2^{n-1}$ .

**Example:** To perform 7-3 using 2's complement addition

If we ignore the carry-out from the fourth bit position in this addition, we obtain the correct answer.

Few more examples:

| (a) | 0 0 1 0<br>+ 0 0 1 1      | (+2)<br>(+3) | <b>(</b> b <b>)</b> | 0100<br>+ 1010       | (+4)<br>(-6) |

|-----|---------------------------|--------------|---------------------|----------------------|--------------|

|     | 0101                      | (+5)         |                     | 1110                 | (-2)         |

| (c) | 1 0 1 1<br>+ 1 1 1 0      | (-5)<br>(-2) | (d)                 | 0111<br>+ 1101       | (+7)<br>(-3) |

|     | 1001                      | (-7)         |                     | 0100                 | (+4)         |

| (e) | $1\ 1\ 0\ 1$<br>- 1 0 0 1 | (-3)<br>(-7) | $\Rightarrow$       | 1 1 0 1<br>+ 0 1 1 1 |              |

|     |                           |              |                     | 0100                 | (+4)         |

**Sign Extension:** We often need to represent a value given in a certain number of bits by using a larger number of bits. For a positive number, this is achieved by adding 0s to the left. For a negative number in 2's-complement representation, the leftmost bit, which indicates the sign of the number, is a 1. A longer number with the same value is obtained by replicating the sign bit to the left as many times as needed.

**Overflow in Integer Arithmetic:** Using 2's-complement representation, n bits can represent values in the range  $-(2^{n-1})$  through  $+2^{n-1}$ . For example, the range of numbers that can be represented by 4 bits is -8through +7. When the actualresult of an arithmetic operation isoutside the representable range, an arithmetic overflow has occurred.

#### Introduction to adder circuits:

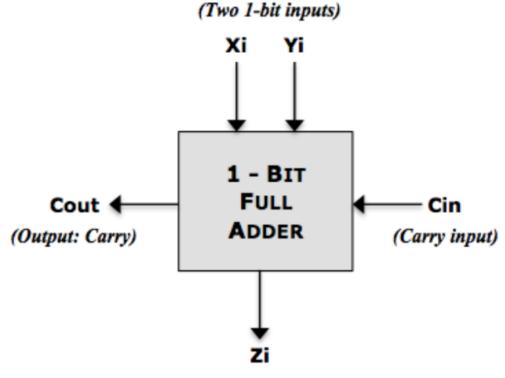

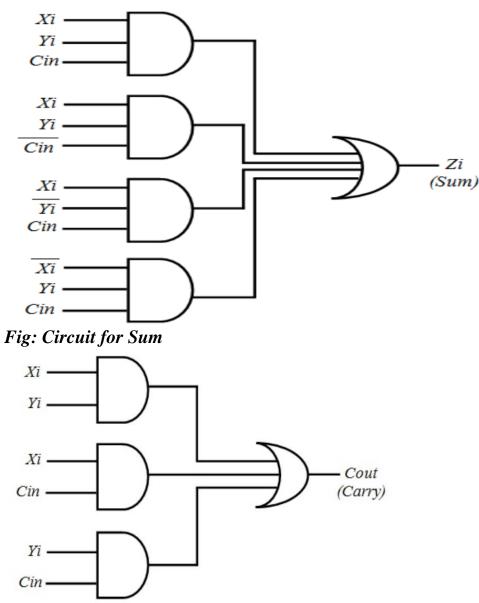

## **ONE BIT ADDITION: FULL ADDER**

- 1) It is a 1-bit adder circuit.

- 2) It adds two 1-bit inputs Xi & Yi, along with a Carry Input Cin.

- 3) It produces a sum Zi and a Carry output Cout.

- 4) As it considers a carry input, it can be used in combination to add large numbers.

- 5) Hence it is called a Full Adder.

(Output: Sum)

## Inputs bits: Xi and Yi. Input Carry: Cin

## Output (Sum): Zi Output (Carry): Cout

# Formula for Sum (Zi)

$Zi = Xi \oplus Yi \oplus Cin$  $\therefore Zi = Xi \cdot Yi \cdot Cin + Xi \cdot Yi \cdot \overline{Cin} + Xi \cdot \overline{Yi} \cdot Cin + \overline{Xi} \cdot Yi \cdot Cin$

# Formula for Carry (Cout)

$Cout = Xi \cdot Yi + Xi \cdot Cin + Yi \cdot Cin$

Fig: Circuit for carry

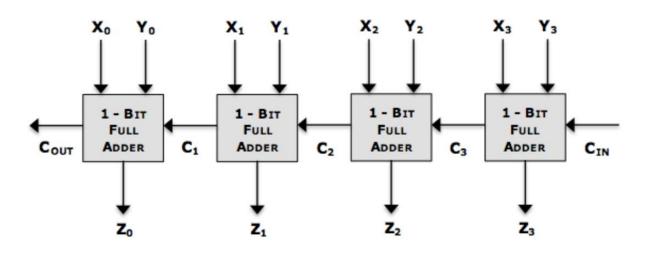

# **RIPPLE CARRY ADDER ( For Multiple bit addition ):**

1)A Full Adder can add two "1-bit" numbers with a Carry input.

2) It produces a "1-bit" Sum and a Carry output.

3) Combining many of these Full Adders, we can add multiple bits.

4) One such method is called Serial Adder.

5) Here, bits are added one-by-one from Least significant bit(LSB) onwards.

6) The carries are connected in a chain through the full adders. The Carry of each stage is propagated (Rippled) into the next stage.

7) Hence, these adders are also called Ripple Carry Adders.

Advantage: They are very easy to construct.

**Drawback:** As addition happens bit-by-bit, they are slow.

8) Number of cycles needed for the addition is equal to the number of bits to be added.

Inputs:

Assume X and Y are two "4-bit" numbers to be added, along with a Carry input CIN. X = X0 X1 X2 X3 (X0 is the MSB ... X3 is the LSB) Y = Y0 Y1 Y2 Y3 (Y0 is the MSB ... Y3 is the LSB) CIN = Carry Input Outputs: Assume Z to be a "4-bit" output, and COUT to be the output Carry

Z = Z0 Z1 Z2 Z3 (Z0 is the MSB ... Z3 is the LSB)(Here Z represents the sum) COUT = Carry Output

Fig:4-bit Ripple Carry Adder

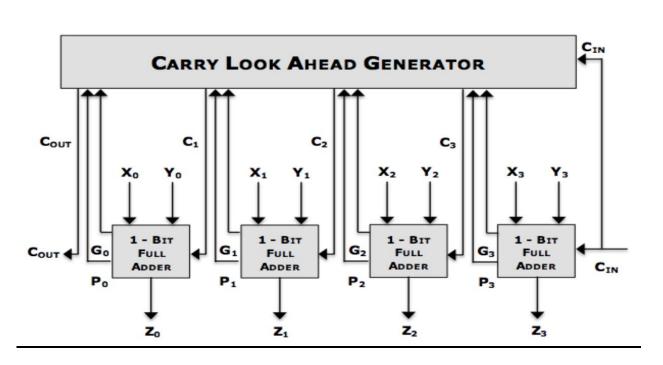

# **Carry Look ahead Adder(For multiple bit Addition):**

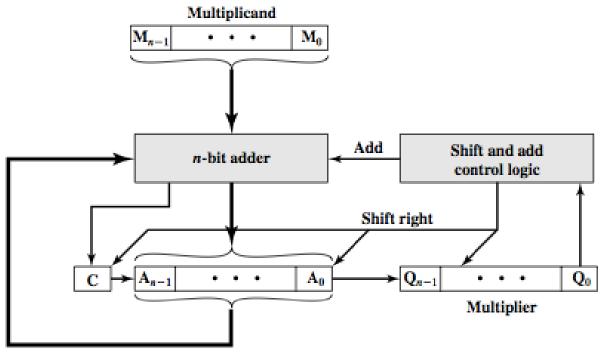

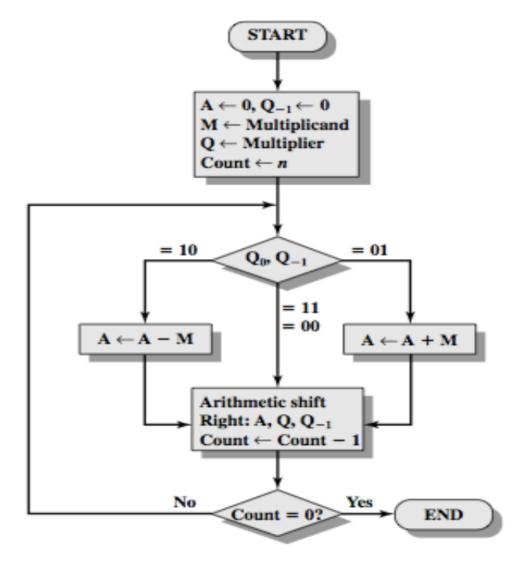

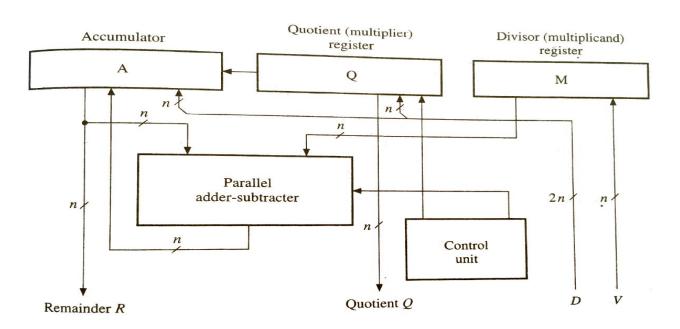

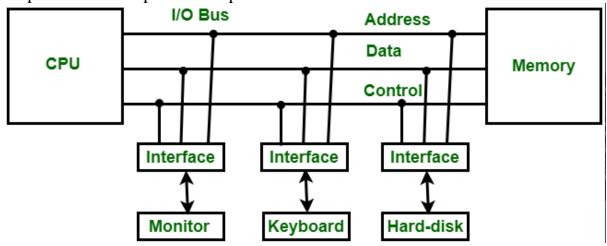

1) This is also called as parallel adder. It is used to add multiple bits simultaneously.